# Electrical characteristics of atomic layer deposited Au/Ti/Al<sub>2</sub>O<sub>3</sub>/*n*-GaAs MIS structures over a wide measurement temperature

A. TURUT<sup>a</sup>, A. KARABULUT<sup>b</sup>, H. EFEOĞLU<sup>c</sup>

- <sup>a</sup>Istanbul Medeniyet University, Faculty of Engineering and Natural Sciences, Engineering Physics Department, TR-34730 Istanbul – Turkey

- $^{b}$ Sinop University, Faculty of Engineering, Department of Electrical and Electronics Engineering, Sinop-Turkey

- <sup>c</sup>Atatürk University, Faculty of Engineering, Department of Electrical and Electronics Engineering, TR-25240 Erzurum, Turkey

We have prepared the Au/Ti/Al<sub>2</sub>O<sub>3</sub>/n-GaAs structures and investigated their current-voltage (I-V) characteristics with the temperature (in 20-320K range) as a parameter, and current-temperature (I-T) characteristics with bias voltage as a parameter. The ultrathin Al<sub>2</sub>O<sub>3</sub> metal-oxide layer on the n-GaAs substrate has been formed by atomic layer deposition (ALD) method. Ti(10nm) rectifying contacts have been fabricated on Al<sub>2</sub>O<sub>3</sub>/n-GaAs structure by DC magnetron sputtering. The ideality factor value has remained between 1.10 -1.06 from 130 K to 320 K. The barrier height (BH) value has increased with a slope of  $\alpha$  = -0.31 meV/K from 320 K to 110 K. Then, it has been seen that the decrease in the BH value from 110 K to 20 K obeys a double Gaussian distribution (GD) of the BHs due to the BH inhomogeneity. The experimental I-T characteristics have been interpreted by plotting the theoretical I-T characteristics with and without the GD based on the TE current theory at each bias voltage. Moreover, the BH values have been also determined from the Richardson curves plotted using the I-T data at each forward and reverse bias voltage. It has been observed that the BH reduction is higher under reverse bias voltage than under forward bias voltage regime due to the barrier inhomogeneity which is not recommended for the Schottky diode being a rectifying device.

(Received April 12, 2016; accepted June 7, 2017)

Keywords: Metal/Insulating layer/semiconductor (MIS) structures, Atomic layer deposition (ALD), Inhomogeneous barrier height, GaAs semiconductor, current-voltage of MIS structures

# 1. Introduction

Metal-semiconductor (MS) rectifying or ohmic contacts are of vital importance for device applications such as photovoltaic solar cells, p-n junctions, bipolar transistors, metal-semiconductor field effect transistors metal-oxide-semiconductor (MESFETs) and (MOSFETs) [1-11]. The ultrathin layers formed by atomic layer deposition (ALD) have found applications such as buffer layers for the growth of high quality materials in the formation of thin films and insulators for thin film transistors, interfacial layers for MOSFET transistors and high-electron mobility transistors, surface passivation layers of channel-FETs [4-13]. The ALD is a vapor-phase thin film deposition method characterized by alternating exposure cycles of chemical species with self-limiting surface reactions. The films with accurate and excellent thickness control and uniform over large substrate areas can be produced by the ALD method [1-3]. As interfacial layer, the metal-oxide Al<sub>2</sub>O<sub>3</sub> is an attractive candidate with a dielectric constant of 9.1 and a wide band-gap of 6.6 eV [1, 2, 9-11]. Integration of ALD oxides with GaAs or other inorganic semiconductors enables lower gate leakage currents, high breakdown voltages, and improved surface passivation [1-6].

We have prepared the Au/Ti/Al<sub>2</sub>O<sub>3</sub>/n-GaAs MIS structures utilizing ALD-grown Al<sub>2</sub>O<sub>3</sub> metal oxide interfacial layer. Ti(10 nm) Schottky contacts were made using magnetron DC sputter technique, and Au(50 nm) metallic layer was evaporated as a top layer on the Ti/n-GaAs structure in high vacuum system of 10-6 Torr. Au thin films are more often used as a top layer to protect other metallic layers and as cap-layer to prevent the oxidation of the Schottky metal. We have investigated the current-voltage characteristics (I-V) in the measurement temperature range of 20-320 K with steps of 10 K. Furthermore, the current versus temperature (I-T)characteristics have been also investigated with bias voltage as a parameter in the measurement temperature range of 20-320 K. Furthermore, the fact that he BH value sharply decreases due to the barrier height inhomogeneity from 110 K to 20 K has been explained by a double Gaussian distribution (GD) of the BHs. Moreover, the barrier height (BH) values have been also determined from Richardson curves at each forward and reverse bias voltage. Thus, the BH versus bias voltage plots have ben been drawn and established the BH reduction versus band bending  $(V_{bb})$  plots for reverse and forward bias voltage. Thus, one might reach the conclusion how the BH reduction occurs under forward bias or under reverse bias.

As known, an ideal rectifying device needs a low-barrier contact under forward bias and a high-barrier contact under reverse bias [12,13], that is, the effective BH should be higher under reverse bias than under forward bias, but an inhomogeneous Schottky contact may behave like a high-barrier contact under forward bias and a low-barrier contact under reverse bias due to the pinch-off effect which is not recommended for the Schottky diode as a rectifying device [12,13].

# 2. Experimental details

The Au/Ti/Al<sub>2</sub>O<sub>3</sub>/n-GaAs MIS structures were fabricated using n-type single crystals GaAs wafer with (100) surface orientation, having thickness of 300 µm,  $6.8 \times 10^{15}$  cm<sup>-3</sup> carrier concentration ( $N_D$ ) and 1.2  $\Omega$  cm resistivity (given by the manufacturer). Before the SBDs fabrication process, the samples were ultrasonically degreased by dipping into acetone for 2 minutes and in propanol for 2 minutes, respectively and then, rinsed in DI water of resistivity of 18 M $\Omega$  cm and dried under N<sub>2</sub> flow. After surface cleaning of n-GaAs, high purity Indium (99.999%) with a thickness of about 2000 Å was coated to the back of the *n*-GaAs wafer for making ohmic contacts by the thermal evaporation at a base pressure about 10<sup>-6</sup> Torr. Low ohmic contact to n-GaAs was obtained by annealing at 385 °C for 3 min under dry nitrogen flow. The ALD of Al<sub>2</sub>O<sub>3</sub> thin films was carried out in Cambridge Nanotech Savannah 100 reactor. The Al<sub>2</sub>O<sub>3</sub> deposition was performed at 200 °C, using trimethylaluminum (TMA) (Al precursor), and water (oxygen precursor), for a total of 30 cycles. Standard photolithography technique was used for pattern fabrication on GaAs. Ti(10 nm) Schottky contacts were made using magnetron DC sputter technique, and Au(50 nm) to protect the Ti metallic layer was evaporated as a top layer on the Ti/n-GaAs structure in high vacuum system of 10<sup>-6</sup> Torr. Finally the photoresist was removed by washed with DI water and then with N2. All the electrical characterizations were carried out using Keithley 2400 current source and 6514 electrometer.

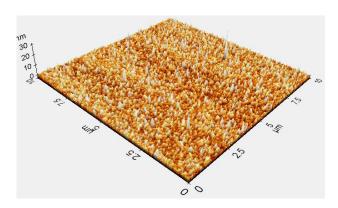

Fig. 1. AFM surface image with 3D for 3 nm thick Al<sub>2</sub>O<sub>3</sub> layer on the GaAs substrate

Temperature-depended measurements were carried out using ARS closed cycle helium cryostat in 20-320K range. Surface roughness was measured using Nano-Magnetics-AFM with tapping mode. Fig. 1 shows the AFM surface image with 3D for  $\sim$ 3 nm thick Al $_2$ O $_3$  layer on GaAs substrate. The Al $_2$ O $_3$  layer surface on GaAs has root-mean-square (RMS) roughness value of 0.904 nm which is a reasonable smooth.

### 3. Results and discussion

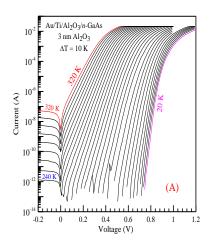

Fig. 2 shows the current-voltage (I-V) characteristics of one of the Au/Ti/Al<sub>2</sub>O<sub>3</sub>/n-GaAs MIS structures in the measurement temperature range of 20-320 K. The reverse bias current could only be measured in temperature range of 240-320 K because the reverse current is below the detection limit of the I-V measurement equipment at lower temperature. It is assumed that the forward bias current through a thin interfacial layer is due to thermionic emission current and it can be expressed as [14-16]

$$I = I_0 \exp\left(\frac{qV}{nkT}\right) \left[1 - \exp\left(-\frac{qV}{kT}\right)\right] , \qquad (1)$$

where

$$I_0 = SA^* \kappa_n T^2 \exp\left(-\frac{q\Phi_b}{kT}\right) , \qquad (2)$$

is the saturation current density,  $\Phi_b$  is the effective barrier height at zero bias in a SBD without the interfacial layer, n is an ideality factor,  $A^*$  is the effective Richardson constant and equals to 8.16 Acm<sup>-2</sup>K<sup>-2</sup> for n-type GaAs, S is the Schottky contact area,  $\kappa_n$  is the transmission coefficient the across interfacial layer and is given by

$$\kappa_n = \exp\left(-\frac{4\pi\delta}{h} \left(2m * \chi\right)^{1/2}\right) = \exp\left(-a\delta(\chi)^{1/2}\right), \quad (3)$$

where  $a\delta(\chi)^{1/2}$  is the electron tunneling factor,  $a=\frac{4\pi}{h}(2m^*)^{1/2}$  is a constant dependent on effective mass,  $m^*=0.067m_0$  is the effective tunneling mass of electrons,  $\chi$  is the effective BH presented by the thin interfacial layer or the energy difference between the conduction band edges of the semiconductor and the interfacial layer, and  $\delta$  is the thickness of the interfacial layer. Eq.(1) and thus Eq.(2) are the standard TE equation for Schottky barriers except for the term  $\exp\left(-a\delta(\chi)^{1/2}\right)$  which is the tunneling probability. If the interfacial layer is extremely thin and is transparent to electron, then  $\kappa_n \approx 1$ . Then, Eq.(2) can be written as [14-16]

$$I_0 = SA^*T^2 \exp\left(-\frac{q\Phi_b}{kT}\right) \exp\left(-a\delta(\chi)^{1/2}\right) ,$$

$$kT \ln\left(\frac{A^*ST^2}{I_0}\right) = q\Phi_b + akT\chi^{1/2}\delta$$

(4)

In the usual analyses of the experimental data on Schottky contacts, the BH value is determined from the extrapolated  $I_0$ . However, this is an apparent barrier height  $q\Phi_{b0}$  when an interfacial layer is present. The effective or measured barrier height  $q\Phi_{b0}$  is given by

$$q\Phi_{b0} = kT \ln \left( \frac{A^* A T^2}{I_0} \right) , \qquad (5)$$

where  $\Phi_{b0} = \Phi_{b0}(T)$  is the effective barrier height at zero bias for a SBD with the interfacial layer at each measurement temperature. Thus, from Eqs.(4) and (5), we have

$$q\Phi_{b0}(T) = q\Phi_b + akT\chi^{1/2}\delta .$$

(6)

Fig. 2. (A) Forward bias current-voltage curves for the Au/Ti/A<sub>2</sub>O<sub>3</sub>/n-GaAs structure in the temperature range of 20-320 K with steps of 10 K and the reverse bias current-voltage curves range from 240 to 320 K with steps of 10 K. (B): Semi-logarithmic {I/[1-exp(-qV/kT)]} versus V plots from the reverse bias I-V data in Fig. 2 (A)

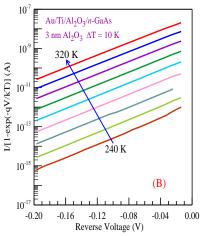

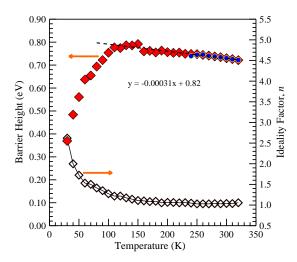

The presence of a linear region over several orders of magnitude in the I-V semi-log plot can be clearly seen from the temperature-dependent forward bias I-V curves in Fig. 2 (A). The deviation of the linearity at high voltages can be attributed to the series resistance coming from the neutral region between the ohmic contact and depletion layer plus  $Al_2O_3$  oxide layer. The ideality factor n values are determined from the slopes of the forward-bias lnI vs V plot using Eq.(1). Fig. 3 shows BH versus temperature plot (solid squares) and ideality factor versus temperature plot (open squares) for the device. The ideality factor value of the device has remained almost constant between 1.10-1.06 in the temperature range of 130-300 K (Fig. 3). Therefore, it can be concluded that the forward bias I-V characteristics follow the well-known thermionic emission (TE) equation in about 130-320 K range. [16-30]. The low values of the ideality factor suggest that the current flow across the device is dominated by the thermionic emission over the BH in this temperature range because the Al<sub>2</sub>O<sub>3</sub> interfacial layer is very thin. As stated in [18], the sputtering can help to remove the defect filled oxide layer and to increase the diode quality. Therefore, the improvement should be expected from the Al<sub>2</sub>O<sub>3</sub> interfacial layer between Au/Ti and the GaAs substrate. That is, one can expected a passivation effect of the Al<sub>2</sub>O<sub>3</sub> layer and the sputter cleaning effect of the surface of the GaAs substrate.

Fig. 3. Barrier height versus temperature plot, the data indicated by solid squares from the forward bias saturation currents in Fig. 2 (A), and the data indicated by solid circles from the reverse bias I-V data in Fig. 2 (B), and ideality factor versus temperature plot (open squares)

The BH values indicated by open triangles in Fig. 3 have been calculated from the intercept of the linear portion of the forward bias I-V plot using equation (2). The BH value has linearly increased from 0.72 eV at 320 K to 0.79 eV at 110 K and then has decreased from 0.79 eV at 110 K to 0.37 eV at 20 K. The linear increase in BH value from 320 to110 K can be attributed to the temperature dependence of the BH or n-GaAs band gap. The BH temperature coefficient,  $\alpha$ , is calculated from the linear

portion by  $\Phi_{b0}(T) = \Phi(T=0) - \alpha T$ . The fitting to  $\Phi_{b0}(T)$  data yields a straight line with the slope of  $\alpha = -0.31$  meV/K. The decrease in the BH value from 110 K to 20 K can be ascribed to the barrier height inhomogeneity which is active especially at low temperature [19-27].

Fig. 2 (B) shows the semi-logarithmic  $\{I/[1-\exp(-qV/kT)]\}$  versus V plots [14] from the reverse bias I-V data in the temperature range of 240-320 K in Fig. 2 (A) for the device. The curves in Figure 2 (B) were formed for calculating the zero bias reverse bias BH values. The zero bias reverse bias BH value at each temperature was determined from the intercept of the reverse-bias  $\ln\{I/[1-\exp(-qV/kT)]\}$  versus V curves using eqn.(1). The data indicated by solid circles in Fig. 3 belong the zero bias reverse bias BH values in the temperature range of 240-320 K. The zero bias BH values from the forward and reverse bias I-V characteristics coincide with each other which indicates the elimination or minimization of the polarity from ions between the  $\operatorname{Al}_2\operatorname{O}_3$  layer and GaAs substrate. [31-34].

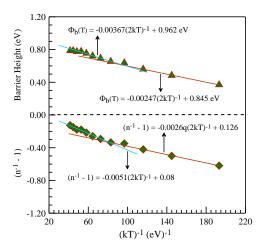

The double linearity of the  $\Phi(T) = \Phi_{b0}(T)$  versus  $(kT)^{-1}$  and  $(n^{-1}-1)$  versus  $(kT)^{-1}$  plots for the BH and ideality factor values at temperatures below 130 K in Fig. 4 says that the decrease in the BH with decreasing temperature may be explained in terms of a double Gaussian distribution (GD) of the Schottky BHs with the mean BH  $\overline{\Phi}_b$  and standard deviation of the distribution,  $\sigma_{s0}$  [19-28]. This model is incorporated on the concept of the spatially inhomogeneous BHs and potential fluctuations at the interface and on a TE mechanism with the GD function. The GD of the BHs yields the following expression for the BH [35-37]:

$$\Phi_{b0}(T) = \overline{\Phi}_{b0} - \frac{q\sigma_{s0}^2}{2kT} \tag{7}$$

where  $\Phi_{b0}(T)$  is the zero-bias BH obtained from the experimental forward bias I-V characteristics (Fig. 2) at each temperature. The variation of the experimental ideality factor n(T) with temperature is given by [35, 36]

$$\left(\frac{1}{n(T)} - 1\right) = -\beta_1 + \frac{q\beta_2}{2kT} \qquad , \tag{8}$$

where parameters  $\beta_1$  and  $\beta_2$  represent the voltage deformation of the BH distribution at an inhomogeneous interface.  $\beta_1$  is the voltage coefficient of the mean BH  $\overline{\Phi}_b$ , and  $\beta_2$  is the voltage coefficient of the standard deviation. The parameters have been obtained from the intercept and slopes of the linear fits to linear regions in Fig. 4 which are plotted from the ideality factor and BH values in 20-130 K range. The  $\Phi(T)$  vs  $(2kT)^{-1}$  and  $(n^{-1}-1)$  versus  $(kT)^{-1}$  plots in Fig. 4 give values of  $\overline{\Phi}_{bo} = 0.96$  eV,  $\sigma_{s0} = 61$  mV and the  $\beta_{1}$ = -0.126 and  $\beta_{2}$ = -0.0026 V for the straight lines on the left side of the graphs in Fig. 4, respectively. Similarly, in Fig. 4, the straight lines on the right side give values of

$\overline{\Phi}_{bo}$  = 0.85 eV,  $\sigma_{s0}$  = 50 mV and  $\beta_{l}$ = -0.08 and  $\beta_{2}$ = -0.0051 V, respectively.

Fig. 4. Experimental apparent barrier height from the saturation currents and ideality factor versus  $(2kT)^{-1}$  plots according to the Gaussian distributions in the temperature range of 20-130 K

From Eqs.(6) and (7), the voltage-independent and voltage-dependent BH can be written as

$$\Phi_b(T) = \overline{\Phi}_{b0} - \frac{q\sigma_s^2}{2kT} + akT\chi^{1/2}\delta$$

(9)

$$\Phi_b(V,T) = \overline{\Phi}_{b0} - \frac{q\sigma_s^2}{2kT} + \left(\beta_1 - \frac{q\beta_3}{2kT}\right)V + akT\chi^{1/2}\delta$$

(10)

respectively. The presence of an interfacial layer at MS interface has been also taken into account here [Eqs. (9), (10)]. This bias dependence of BHs in the distribution through mean BH and standard deviations leads to the bias-dependent ideality factor in inhomogeneous Schottky diodes [35-45].

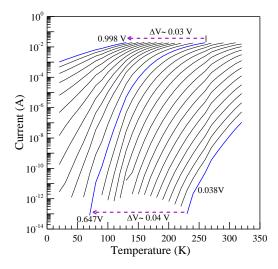

Fig. 5 shows the experimental current versus temperature curves with the applied voltage as a parameter for the device. The bias voltage ranges from 0.038 V to 0.647 V with steps of about 0.04 V and from 0.647 V to 0.988 V with steps of about 0.03 V. As seen from the I-V curve at each temperature in Fig, 2, the deviation of linearity or the downward concavity due to the series resistance begins at 0.72 V for 100 K and at 0.84 V for 20 K. Therefore, we can be said that the portion above 0.84 V of the experimental current versus temperature curves in Fig. 5 only reflect the temperature-dependent behavior of the GaAs bulk plus the Al<sub>2</sub>O<sub>3</sub> layer. That is, when Fig. 5 is considered together with Fig. 2, it can be said that the current versus temperature curves in Figure 5 are affected from the series resistance of the GaAs bulk plus the Al<sub>2</sub>O<sub>3</sub> layer above ~10<sup>-3</sup> A.

Fig. 5. Experimental Current versus temperature plots as a function of the applied forward voltage

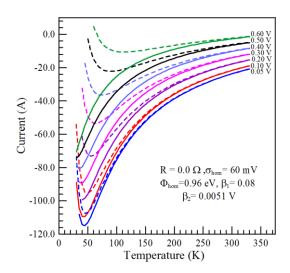

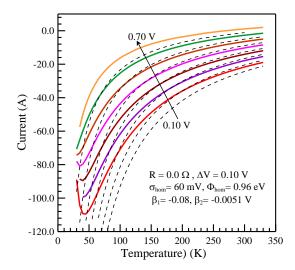

Before interpreting the temperature-dependent behavior of the experimental current curves, let us study to obtain the theoretical I-T curves at each bias voltage using Eq.(6) or (9) or (10) in Eq.(1). The obtained theoretical curves are given in Figs. 6 and 7. When considering the theoretical calculations, it is seen that the mean BH  $\Phi_{b0}$ in Eq.(9) is constant and the second term on the right side in the equation increases with a decrease in the temperature, therefore the apparent BH value decreases with decreasing the temperature. The apparent BH in Eq.(6) is the temperature-dependent due to the second term on the right side in the equation, therefore the apparent BH value decreases with decreasing the temperature. However, the contribution of this term to the apparent BH value increases with increasing temperature, for example  $2.24 \times 10^{-3}$ ,  $9.21 \times 10^{-3}$  and  $1.41 \times 10^{-2}$  eV for  $\chi = 0.032$  eV at 20 K, 60K and 130 K, respectively.

Fig. 6. Theoretical current versus temperature curves as a function of the applied voltage using eqn. (9) or (10) in eqn. (1), dashed lines for eqn. (9), and solid lines for eqn.(10)

Fig. 7. Theoretical current versus temperature curves as a function of the applied voltage using eqn. (6) or (10) in eqn.(1), dashed lines for eqn.(6) or for TE equation, and solid lines for eqn.(10).

As can be seen from the theoretical curves in Figs. 6 and 7, the current at each bias increases with increasing temperature which is in good agreement with the thermal activation mechanism of a Schottky diode [36-50] and it trends to saturate after a given temperature although R=0. That is, the saturation behavior of the current in Figure 6 and 7 at high temperatures is not only due to the series resistance. When the experimental *I-T* curves at each bias voltage in Fig. 5 are compared with the corresponding theoretical *I-T* curves in Figs. 6 and 7, it is seen that the shape of the experimental *I-T* curves is similar to that of the curves plotted using Eq.(10) in Fig. 7.

However, the apparent BH in Eq.(10) is the bias-dependent due to the third term on the right side in the equation, and therefore, the disruptions resulting in the Eq.(9) are compensated at least partially as Eq.(10) has been used. It is clearly seen from Fig. 6 that the curves with the dashed line are generated using Eq.(9) and the curves with the solid lines are obtained using Eq.(10). The current curves with dashed line in Figure 6 increase with the decrease of temperature at low temperature region, that is, it shows the negative thermal activation behavior. As can be seen from the current curves in Fig. 6, the negative thermal activation behavior in the current curves with dashed line is compensated at least partially in the solid-line current curves plotted using Eq.(10), due to the bias-dependent third term on the right side in Eq.(10).

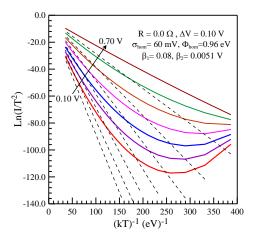

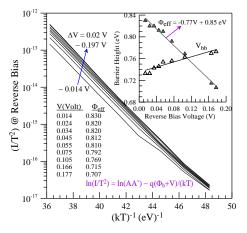

Fig. 8 shows the theoretical Richardson  $\ln(I/T^2)$  versus  $(kT)^{-1}$  curves with the forward bias voltage as a parameter. The curves with the dashed line and solid line in the figure have been obtained using Eqs.(6) or (10) in Eq.(1) respectively.

Fig. 8. Theoretical Richardson curves as a function of the applied voltage using eqn. (6) or (10) in eqn.(1) in the temperature range of 30-230 K, dashed lines for eqn.(6) or for TE equation, and solid lines for eqn.(10)

The theoretical Richardson curves in Fig. 8 have been plotted for the interpretation of the experimental Richardson curves in Fig. 9. As mentioned above, if  $\Phi_h(V,T)$  given in Eq.(10) is used in place of  $\Phi_h$  in Eq.(1), then Eq.(1) is called the modified TE current equation with the GD function which is given for Schottky contacts with the spatially inhomogeneous. As can be seen from Fig. 8, the theoretical curves with the solid line below 0.70 V deviate of the linearity in at low temperatures, but they trends to be linear with increasing bias voltage over the whole measurement temperature for all bias voltages above 0.60 V. When the bias-independent BH equation (9) was used, an excessive deviation from linearity is observed at low temperatures and at high bias voltages (these plots are not given here). It has been mentioned above that the experimental apparent BH (Fig. 4) determined from the saturation current (V=0 volts) for each temperature (Fig. 2) decreases with decreasing temperature obeying to the Gaussian distribution of the BHs in the temperature range of 20-130 K.

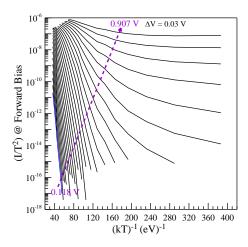

Fig. 9. Experimental Richardson  $(I/T^2)$  versus  $(kT)^{-1}$  plots as a function of the forward applied voltage in the temperature range of 40-320 K

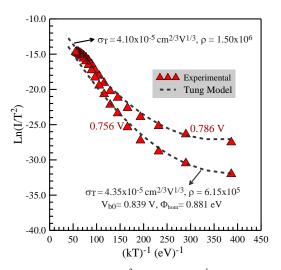

Thereby, the explanations above for Figs. 4 and 8 or Fig. 10 should be not confused with each other. As can be seen, Fig. 10 shows the experimental (indicated with triangles) and theoretical (the dashed lines) Richardson  $(I/T^2)$  versus  $(kT)^{-1}$  curves for the forward applied voltage of 0.756 and 0.786 V. Thus, it can be said that the deviation of the linearity observed at low temperatures and high bias voltages in the experimental Richardson curves may be attributed to the fact that the current through the diode flows preferentially through the lower barrier-small local regions called as the patches [12, 13, 38-50].

Fig. 10. Richardson (I/T<sup>2</sup>) versus (kT)<sup>-1</sup> plots at the forward applied voltage of 0.756 and 0.786 V, Triangles: the experimental data, the dashed lines: theoretical curves according to patch model [12]

According to Tung's model, the TE current expression can be modified for the case of a configuration of low circular BH-patches [12, 13]. Thus, the current through the junction formed from the low-SBH patches can be approximately described as [12]:

$$I = A_{eff} \rho A * T^{2} \exp\left(-\frac{\Phi_{eff}}{kT}\right) \left[\exp\left(\frac{(V - IR_{s})}{kT}\right) - 1\right] (11)$$

Thus, we have rewritten Eq.(1) for the total current flowing through the diode taking into account the effective area of the diode given by  $\rho A_{eff}$ ,  $\rho$  is the number of patches covering area of the diode as free parameter, the product  $\rho A_{eff}$  represents the value of the total effective area of the patches contributing to the current transport. The effective area of a low-BH patch  $A_{eff}$  can be expressed as [12]

$$A_{eff} = \frac{8\pi\sigma_T^2}{9} \left(\frac{\eta}{V_{b0} - V}\right)^{1/3} \tag{12}$$

However, according to Tung's patch model, the ideality factor and effective BH are given by [12]

$$n \approx 1 + \frac{\sigma^2 (V_{b0} - V + IR_s)^{-1/3}}{3kT\eta^{2/3}},$$

(13)

$$\Phi_{eff} = \Phi_{hom} - \frac{\sigma^2}{2kT} \left( \frac{V_{b0} - V + IR_s}{\eta} \right)^{2/3} , \qquad (14)$$

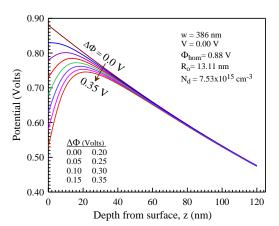

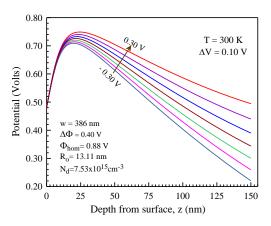

respectively, where  $\Phi_{\mathrm{hom}}$  is the homogeneous BH,  $\eta$  $=\varepsilon_{\rm s}\varepsilon_{\rm o}/qN_{\rm d}$ ,  $\varepsilon_{\rm s}$  and  $N_{\rm d}$  are the dielectric constant and the dopant density of the semiconductor substrate.  $V_{b0}$  is the zero bias band bending of the uniform barrier. As can be seen from Eq.(12),  $A_{eff}$  depends on the bias voltage. For small and circular patches, Tung [12] assumes a GD of low-SBH circular patches characterized by a distribution with standard deviation  $\sigma_{\rm T}$  and the interaction of the patch with the surrounding depletion region causes a pinch-off or saddle point in the potential barrier away from the interface [12, 13, 17]. Fig. 10 has been plotted by considering Eqs.(11)-(14) according to Tung's model [12]. A lateral homogeneous BH value of 0.88 eV has been used in the equations above. The dashed lines in Figure 10 display the modeling to the experimental Richardson  $(I/T^2)$ versus  $(kT)^{-1}$  curves at the forward voltages of 0.756 and 0.786 V. It has been obtained the values of 4.35x10<sup>-5</sup> cm<sup>2/3</sup>V<sup>1/3</sup>, 1.44x10<sup>-11</sup> cm<sup>2</sup> and 6.15x10<sup>5</sup> for  $\sigma_T$ ,  $A_{eff}$  and  $\rho$  at 0.756, respectively, the values of 4.10x10<sup>-5</sup> cm<sup>2/3</sup>V<sup>1/3</sup>,  $1.14 \times 10^{-11}$  cm<sup>2</sup> and  $1.50 \times 10^{6}$  at 0.786 V, respectively. Furthermore, the effective area of the diode,  $\rho A_{eff}$ , has been obtained as  $8.24 \times 10^{-6}$  cm<sup>2</sup> and  $1.71 \times 10^{-5}$  cm<sup>2</sup> for 0.756 and 0.786 V, respectively, because  $A_{eff}$  depends on the bias voltage. The Eq.( 11) was modeled with number generation for varying parameters of  $\sigma_T$ ,  $A_{eff}$  and  $\rho$  with Mathcad software. We did not use the fitting methods with error analysis because the equation involves same parameters in exponential part. So the iterative approach with fitting methods is not successive for this case.

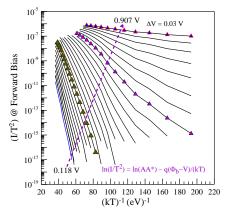

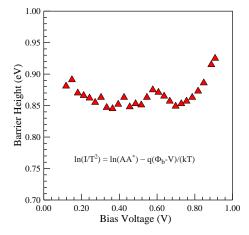

The linear portion of each experimental curve in Fig. 9 has been chosen for obtaining the bias-dependent BH, and thus Fig. 11 has been generated. Similarly, the Richardson  $(I/T^2)$  versus  $(kT)^{-1}$  curves have been also plotted for calculating the reverse bias dependent BH. The reverse bias-dependent BH versus bias voltage plot is given in the inset of Fig. 12. The forward bias-dependent BH versus bias voltage plot is given in Fig. 13. Moreover, the inset of Fig. 12 also shows the band bending  $(V_{bb})$ versus reverse applied voltage plot. The temperature dependence of the Fermi potential in the calculations was neglected, and the value of  $V_n$ = 0.11 V at 300 K was only used. From the minimum and maximum values of 0.71 eV and 0.83 eV, a mean value of 0.79 eV with a standard deviation value of 46 meV has been obtained from the reverse bias-dependent BH data in Fig. 12. From the minimum and maximum values of 0.85 eV and 0.93 eV, a mean value of 0.87 eV with a standard deviation value of 19 meV has been obtained from the forward biasdependent BH data in Fig. 13.

Fig. 11. Experimental Richardson (I/T<sup>2</sup>) versus (kT)<sup>-1</sup> curves plotted by taking for calculation of the barrier height at each forward bias voltage

Fig. 12. Experimental Richardson  $(I/T^2)$  versus  $(kT)^{-1}$  plots as a function of the reverse applied voltage for  $Au/Ti/A_2O_3/n$ -GaAs structure. The inset shows barrier height and band bending  $(V_{bb})$  versus reverse applied voltage plot. Fermi potential  $V_n = 0.11 \text{ V}$  at 300 K. The temperature dependence of the Fermi potential was neglected here.

Fig. 13. Barrier Height as a function of the forward applied voltage from experimental Richardson  $(I/T^2)$  versus  $(kT)^{-1}$  plots in Fig. 11

In the reverse bias case, the effective BH decreases with the voltage, leading to unsaturated reverse current, as can be seen in the inset of Fig. 12. As mentioned in refs.[12, 13, 17], the saddle-point potential energy increases with an applied forward bias and decreases with the reverse bias [12, 13, 17]. An increase in the effective SBH is due to rise in the saddle point potential under forward applied bias that controls the current transport with the applied voltage [12, 13]. That is, the model [12, 13] says that the effective BH is higher under forward bias than under reverse bias. The effective area of a low-BH patch  $A_{eff}$  is about obtained as  $1.34 \times 10^{-11}$  cm<sup>2</sup> at 0.0 V from data above, thus a small circular patch radius = 13.11 nm using the modeling parameters on Figs. 14 and 15. This patch radius value is about 30 times lower than the depletion layer width w. The diffusion potential distributions for patches can be determined using equation (6) in ref.[12]. Fig. 14 shows the diffusion potential distributions for patches with various Schottky BH difference, from the barrier difference of 0.0 V to the barrier difference of 0.35 V with the steps of 0.05 V, as a function of the distance z from the MS interface towards the semiconductor. The critical value of the barrier difference for the potential pinch-off is about 0.052 V here. As well-know, when the BH difference is less than critical value, there is no potential pinch-off. As can be seen from Fig. 14, the pinch-off degree increases with an increase in the barrier height difference. Fig. 15 shows the diffusion potential distributions of low-SBH circular patches for different bias voltages across the MS contact, from the reverse bias of -0.30 V to forward bias of 0.30 V with the steps of 0.10 V, as a function of the distance z from the MS interface towards the semiconductor. As seen from the Figure, the saddle point potential slowly increases with increasing forward bias, and slowly decreases with reverse bias. Ru et all. [13] have showed that the pinch off is stronger under forward bias voltage than under reverse bias voltage, considering the model of Tung [12].

Fig. 14. Diffusion potential distributions for low-SBH circular patches with various Schottky barrier height difference, the barrier difference of 0.0 V to the barrier difference of 0.35 V with the steps of 0.05 V, as a function of the distance z from the MS interface towards the semiconductor

Fig. 15. Diffusion potential distributions for low-SBH circular patches patches under the bias voltage, from the reverse bias of -0.30 V to forward bias of 0.30 V with the steps of 0.10 V, as a function of the distance z from the MS interface to the inside of the semiconductor

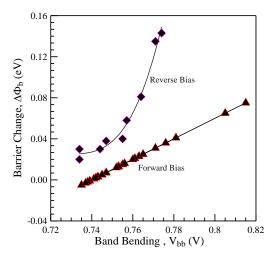

Fig. 16. Experimental Barrier Height versus band bending curves from the bias dependent forward and reverse bias barrier height data in Figures 10 and 11 plots for Au/Ti/A<sub>2</sub>O<sub>3</sub>/n-GaAs structure

We can now give the BH reduction or change with the reverse and forward bias from the above information in Fig. 16. It has been seen from Fig. 16 that the BH reduction is higher under reverse bias voltage than under forward bias voltage. The results we have found for the Au/Ti/Al<sub>2</sub>O<sub>3</sub>/n-GaAs structure are in agreement with those for NiSi/n-Si Schottky diodes [13] and with the model of Tung [12] who suggest that the pinch off is stronger under forward bias voltage than under reverse bias voltage. However, it has been desired from a technological point of view that a device always should be a low-barrier rectifying contact under forward bias voltage and a highbarrier rectifying contact under reverse bias voltage. Thus, it can be said that the pinch-off effect is not recommended for the Schottky diode as a rectifying device because the pinch-off model says that an inhomogeneous Schottky contact behaves like a high-barrier contact under forward bias voltage and a low-barrier contact under reverse bias voltage [12, 13].

### 4. Conclusions

It has been observed from the experimental results above that the I-V characteristics of the device have followed the TE current model in 130-320 K range which is confirmed by the ideality factor values in 1.10-1.06 range although the device is a MIS SBD with the Al<sub>2</sub>O<sub>3</sub> interfacial layer. While the BH value from the forward bias I-V characteristics has increased with the slope of  $\alpha$  = -0.31 meV/K in 110-320 K range, and it has decreased obeying the GD of barrier heights based on the modified TE current equation in the temperature in 20-110 K range. In the current-temperature (I-T) curves at each bias voltage, the current has increased with increasing temperature and tend to saturate at further temperatures. The experimental results have shown that the barrier height strongly depends on the spatial inhomogeneity and thus the bias voltage. We have shown that the shapes of the experimental *I-T* curves at each bias voltage are in similarity with those obtained from the modified TE with GD and conventional TE current models. However, the forward and reverse bias-dependent BH data from the *I-T* curves have shown that the device behaves like a high-barrier contact under forward bias voltage and a low-barrier contact under reverse bias voltage due to the inhomogeneous Schottky barrier height which is understandable with patch pinch-off effects based on Tung's model.

## Acknowledgements

The current-voltage measurements were made at Department of Electrical-Electronics Engineering, Faculty of Engineering, Atatürk University Turkey.

# References

- [1] S. J. Lim, S. Kwon, H. Kim, Thin Solid Films 516, 1523 (2008).

- [2] C. Ozgit, I. Donmez, M. Alevli, N. Biyikli, Thin Solid Films **520**, 2750 (2012).

- [3] M. Ritala, M. Leskela, Handbook of Thin Film Material Vol.1: Deposition and Processing of Thin Films, (Ed: H.S. Nalwa), Academic Press, Finland, 2002.

- [4] O. Pakma, N. Serin, T. Serin, Ş. Altındal, J. Appl. Phys. 104, 014501 (2008).

- [5] B. Kınacı, S.Ş. Cetin, A. Bengi, S. Ozcelik, Mater. Sci. Semicon. Process. **15**, 531 (2012).

- [6] S. Sönmezoglu, S. Akın, Curr. Appl. Phys. 12, 1372 (2012).

- [7] A. Kumar, P. C. Srivastava, J. Electron. Mater. 43, 381 (2014).

- [8] W. Mönch, J. Vac. Sci. Technol. B 17, 1867 (1999).

- [9] Y. Liu, S. Shen, L.J. Brillson, R.G. Gordon, Appl. Phys. Lett. 98, 122907 (2011).

- [10] R.D. Long, A. Hazeghi, M. Gunji, Y. Nishi, P.C. McIntyre, Appl. Phys. Lett. **101**, 241606 (2012).

- [11] R. D. Long, P. C. McIntyre, Materials 5, 1297 (2012).

- [12] R. T. Tung, Phys. Rev. B 45, 13509 (1992).

- [13] G. P. Ru, R. L. Van Meirhaeghe, S. Forment, Y. L. Jiang, X. P. Qu, S. Zhu, B. Z. Li, Solid-State Electron 49, 606 (2005).

- [14] H. C. Card, E. H. Rhoderick, J. Phys. D: Appl. Phys. 4, 1589 (1971).

- [15] A. Turut, B. Batı, A. Kökçe, M. Sağlam, N. Yalçın, Phys. Scr. 53, 118 (1996).

- [16] S. Alialy, A. Kaya, E. Maril, Ş. Altındal, İ. Uslu, Philosophical Magazine **95**, 1448 (2015).

- [17] M. Mamor, K. Bouziane, A. Tirbiyine, H. Alhamrashdi, Superlatt. Microstruct. **72**, 344 (2014).

- [18] A. Zussman, J. Appl. Phys. **59**, 3894 (1986).

- [19] O. F. Yuksel, Physica B 404, 1993 (2009).

- [20] J. Osvald, Z.J. Horvath, Appl. Surf. Sci. **234**, 349 (2004).

- [21] K. Ejderha, N. Yıldırm, A. Turut, Eur. Phys. J. Appl. Phys. 68, 20101 (2014).

- [22] A. F. Hamida, Z. Ouennoughi, A. Sellai, R. Weiss, H. Ryssel, Semicond. Sci. Technol.23, 045005 (2008).

- [23] P. M. Gammon, A. Perez-Tomas, V. A. Shah,

O. Vavasour, E. Donchev, J. S. Pang, M. Myronov,

C. A. Fisher, M. R. Jennings, D. R. Leadley,

P. A. Mawby, J. Appl. Phys. 114, 223704 (2013).

- [24] D. A. Aldemir, A. Kokce, A. F. Ozdemir, Microelectronic Engineering 98, 6 (2012).

- [25] B. Boyarbay, H. Cetin, M. Kaya, E. Ayyildiz, Microelectron. Engineer. **85**, 721 (2008).

- [26] O. Gullu, M. Biber, S. Duman, A. Turut, Appl. Surf. Sci. 253, 7246 (2007).

- [27] H. Saghrouni, R. Hannachi, S. Jomni, L. Beji, Physica B 422, 64 (2013).

- [28] J. M. Dhimmar, H. N. Desai, B. P. Mod, J. Nano-and Electronic Phys. **8**(2), 02006 (2016).

- [29] S. R. T. Djiokap, Z. N. Urgessa, C. M. Mbulanga, A. Venter, J. R. Botha, Physica B 480, 68 (2016).

- [30] E. Omotoso, W. E. Meyer, F. D. Auret, A. T. Paradzah, M. Diale, S. M. M. Coelho, P. J. Janse van Rensburg, Mater. Sci. Semicond. Process. 39, 112 (2015).

- [31] K. Ejderha, A. Zengin, I. Orak, B. Tasyurek, T. Kilinc, A. Turut, Mater. Sci. Semiconduc. Process. 14, 5 (2011).

- [32] J. Osvald, J. Kuzmik, G. Konstantinidis, P. Lobotka, A. Georgakilas, Microelectron Eng. **81**, 181 (2005).

- [33] S. N. Mohammad, J. Appl. Phys. 97, 063703 (2005).

- [34] I. Tascioglu, U. Aydemir, S. Altındal, B. Kınacı,S. Ozcelik, J. Appl. Phys. 109, 054502 (2011)

- [35] Y. P. Song, R. L. Van Meirhaeghe, W. H. Laflére, F. Cardon, Solid-St. Electron. 29, 633 (1986).

- [36] J. H. Werner, H. H. Guttler, J. Appl. Phys. **69**, 1522 (1991).

- [37] S. Chand, J. Kumar, Appl. Phys. A 63, 171 (1996).

- [38] N. Yıldırım, A. Turut, V. Turut, Microelectron. Engineer. **87**, 2225 (2010).

- [39] A. N. Bestas, S. Yazıcı, F. Aktas, B. Abay, Applied Surface Science **318**, 280 (2014).

- [40] A. Gümüş, Ş. Altındal, Mater. Sci. Semicond. Process. **28**, 66 (2014).

- [41] M. Saglam, B. Guzeldir, A. Ates, E. Bugur, J. Phys. Chem. Solids **74**, 370 (2013).

- [42] P. Kaushal, S. Chand, J. Osvald, Intern. J. Electron. **100**, 686 (2013).

- [43] M. Soylu, F. Yakuphanoglu, Superlatt. Microstruct. **52**, 470 (2012).

- [44] V. Janardhanam, Y. H. Kil, K. H. Shim, V. R. Reddy, C. J. Choi, Materials Transactions **54**, 1067 (2013).

- [45] H. Efeoglu, A. Turut, Int. J. Modern Phys. B 27, 1350088 (2013).

- [46] F. S. Abu-Samaha, A. A. A. Darwish, A. N. Mansour, Mater. Sci. Semicond. Process. 16, 1988 (2013).

- [47] M. Tahir, M. H. Sayyad, F. Wahab, F. Aziz, M. Shahid, M. A. Munawar, Physica B 426, 6 (2013).

- [48] A. J. Mathai, IEEE Trans. Electron. Dev. **58**, 4283 (2011).

- [49] W. Mönch, Mater. Sci. Semicon. Process. **28**, 2 (2014).

- [50] M. Gülnahar, T. Karacali, H. Efeoglu, Electrochimica Acta **168**, 41 (2015).

<sup>\*</sup>Corresponding author: akerimkara@gmail.com